首页 >> 生活 >

新颖的架构可以减少数字技术中噪声引起的抖动

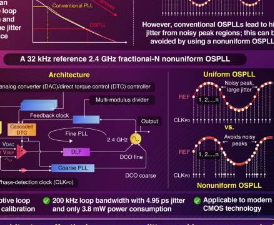

现代电子设备的功效和效率通常取决于它们的信号噪声和抖动。抖动是高频数字信号中信号波形的波动或偏差。有许多传统方法可以减轻抖动并提高设备的性能特征。一种常见的方法是使用过采样锁相环(OSPPL)。OSPLL可以扩展环路带宽并改善抖动性能。

现在,虽然它们具有许多优势,但使用传统的OSPLL会导致噪声峰值区域的高抖动,因为峰值区域具有较小的梯度。传统32kHz信号的缓慢参考斜率会引入较大的抖动,并导致较大的归因时间误差。

迄今为止,这一缺点阻碍了OSPLL的更广泛使用。现在,东京工业大学(TokyoTech)的一组科学家展示了如何通过使用不均匀的OSPLL来避免这种情况。

领导研究团队的KenichiOkada教授进一步解释了这一发展:“我们新颖的过采样架构使用32kHz参考提供了一个低抖动的2.4GHz小数NPLL。传统PLL的环路带宽理论上限制为参考频率的1/10,根据Gardner的稳定性理论。这种窄环路带宽会导致抖动恶化。我们的非均匀过采样PLL可以将环路带宽增加60倍,并且可以有效抑制抖动。

新构思的器件架构允许进行自适应环路增益校准。通过为每个采样点自动执行环路增益校准,可以将抖动降至最低。

“我们的设备的性能突出体现在其200kHz环路带宽和4.95ps抖动。在这些参数下,该设备仅消耗3.8mW的功率。此外,它可以与CMOS技术集成,使其成为一个特别有吸引力的前景-不断发展的电子行业,”他们研究的主要作者东京工业大学的JunjunQiu补充道。

由于减少了抖动和更高更清晰的信号,这种范式转换架构也比传统的OSPLL更经济、更节能。

免责声明:本文由用户上传,与本网站立场无关。财经信息仅供读者参考,并不构成投资建议。投资者据此操作,风险自担。 如有侵权请联系删除!

分享:

最新文章

-

宝子们,杭州 房子装修完成啦!这次要给大家分享几家设计超赞的装修公司哦。它们各具特色,从空间规划到风格...浏览全文>>

-

欲筑室者,先治其基。在上海,装修房子对于每个业主而言,都是极为关键的一步,然而,如何挑选一家值得信赖的...浏览全文>>

-

2025年以来,联通支付严格贯彻落实国家战略部署,以数字和科技为驱动,做好金融五篇大文章,履行支付为民社会...浏览全文>>

-

良工巧匠,方能筑就华居;精雕细琢,方可打造美家。当我们谈论装修公司时,选择一家靠谱可靠的公司是至关重要...浏览全文>>

-

在当今社会,随着城市化进程的高速推进,建筑垃圾的产生量与日俱增。据权威数据显示,我国每年建筑垃圾产生量超 ...浏览全文>>

-

家人们,在上海要装修,选对公司那可太重要了!古语有云:"安得广厦千万间,大庇天下寒士俱欢颜。"一个温馨的...浏览全文>>

-

近年来,新能源汽车市场发展迅猛,各大品牌纷纷推出各具特色的车型以满足消费者多样化的需求。作为国内新能源...浏览全文>>

-

近年来,随着汽车市场的不断变化和消费者需求的升级,安徽滁州地区的宝来2025新款车型在市场上引起了广泛关注...浏览全文>>

-

随着汽车市场的不断变化,滁州地区的消费者对高尔夫车型的关注度持续上升。作为大众品牌旗下的经典车型,高尔...浏览全文>>

-

在2023年,大众探影以其时尚的设计和出色的性能赢得了众多消费者的青睐。作为一款小型SUV,探影凭借其紧凑的车...浏览全文>>

大家爱看

频道推荐

站长推荐

- 安徽滁州途安L新车报价2022款,最低售价16.68万起,入手正当时

- 小鹏G7试驾,新手必知的详细步骤

- 别克GL8预约试驾,4S店的贴心服务与流程

- 安徽阜阳ID.4 CROZZ落地价全解,买车必看的省钱秘籍

- 淮北探岳多少钱 2025款落地价,最低售价17.69万起现在该入手吗?

- 安徽淮南大众CC新款价格2025款多少钱能落地?

- 淮北长安启源C798价格,最低售价12.98万起现在该入手吗?

- 安徽淮南途锐价格,各配置车型售价全解析

- 蒙迪欧试驾预约,4S店体验全攻略

- 沃尔沃XC40试驾需要注意什么

- 滁州ID.4 X新车报价2025款,各车型售价大公开,性价比爆棚

- 试驾思域,快速操作,轻松体验驾驶乐趣

- 试驾长安CS35PLUS,一键搞定,开启豪华驾驶之旅

- 天津滨海ID.6 X落地价限时特惠,最低售价25.9888万起,错过不再有

- 天津滨海凌渡多少钱?看完这篇购车攻略再做决定

- 安徽池州长安猎手K50落地价,买车前的全方位指南

- 山东济南ID.6 CROZZ 2024新款价格,最低售价19.59万起,现车充足

- 试驾海狮05EV,新手必知的详细步骤

- 生活家PHEV多少钱 2025款落地价走势,近一个月最低售价63.98万起,性价比凸显

- 奇瑞风云A9试驾,新手必知的详细步骤